# ECE 320 - Homework #8

Boolean Logic, DTL, TTL Logic. Due Monday, October 21st

#### **Transistor Data Sheets**

- 1) Find the data sheets for a 3904 transistor. From the data sheets, determine

- V<sub>be</sub> @ 20mA

- V<sub>ce(sat)</sub>

- $h_{FE} = \beta$

- $I_{c(max)}$

# **Boolean Logic**

- 2) Design a circuit using NAND gates to implement Y(A,B,C,D) (i.e. circle the 1's)

- 3) Design a circuit using NOR gates to implement Y(A,B,C,D) (i.e. circle the 0's)

| Y(A,B,C,D) |    | CD |    |    |    |

|------------|----|----|----|----|----|

|            |    | 00 | 01 | 11 | 10 |

| АВ         | 00 | 1  | 0  | 1  | 0  |

|            | 01 | 0  | 0  | 0  | 1  |

|            | 11 | Х  | Х  | Х  | Х  |

|            | 10 | 0  | 1  | Х  | Х  |

Problem 2 & 3: Y = f(A, B, C, D)

## **DTL Logic**

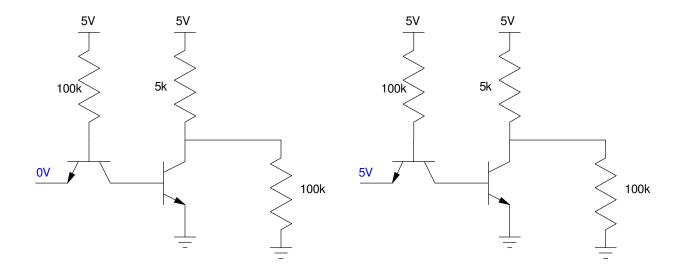

4) Determine the voltages and currents for the following DTL AND gate. Assume 3904 transistors (from problem #1)

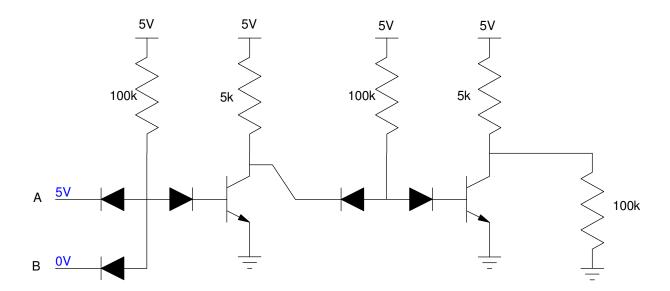

5) Determine the voltages and currents for the following DTL OR gate. Assume 3904 transistors

- 6) Check your analysis for problem #5 (DTL OR) in PartSim (or similar program)

- 7) (Lab): Build a DTL OR gate in lab. Measure

- The votlages when the input is  $\{0V, 0V\}$ ,

- The votlages when the input is { 0V, 5V }, and

- The maximum frequency the logic gate can respond to (apply a square wave at the input)

## **TTL Logic**

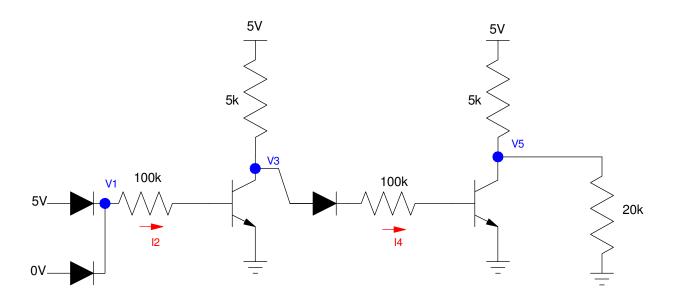

8) Determine the voltages for the following TTL inverter. Assume 2n222 transistors.