# Lag Compensators

## Lag Compensator Design:

Lag compensators serve to increase the DC gain, increasing the error constants and decreasing the tracking error. The idea behind lag compensators is to apply a Band-Aid to a system which is already designed, but does not meet a design criteria for Kp or Kv. In this case, you would like to keep your previous design, but crank up the DC gain.

The form of a lag compensator is

$$K_{lag} = \left(\frac{s+a}{s+0.1a}\right)$$

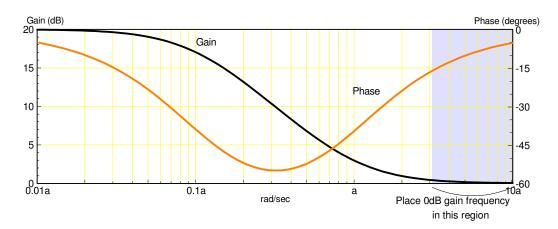

with its frequency response shown below.

Frequency Response of a Lag Compensator

Note that the DC gain will be 10 regardless of how you pick the zero, 'a'. Likewise, this will always increase the value of the error constant by 10x. Also note that

- The gain is always positive. This will push G(s) towards -1 on a Nichols chart, making the system less stable.

- The phase is always negative. This will push G(s) towards -1 on a Nichols chart, making the system less stable.

Since the lag compensator makes the system worse, the design is to

- Pick 'a' as large as possible, making the lag compensator as responsive as possible, but

- Not large enough to affect the system's response.

The standard rule for 'a' is

Pick the zero of the lag compensator to be 1/3rd to 1/10th of the 0dB gain frequency.

Note that even at 1/10th, the phase of the lag compensator is still negative. Letting  $\omega_{0dB} = 1$  and a=0.1,

$$K_{lag}(s) = \left(\frac{s+0.1}{s+0.01}\right)$$

$$K_{lag}(j1) = 1.0049 \angle -5.1^{0}$$

This will hurt your phase margin by 5.1 degrees. If you prefer the 1/3 rule

$$K_{lag}(s) = \left(\frac{s+0.33}{s+0.033}\right)$$

$$K_{lag}(j1) = 1.05 \angle -16.3^{\circ}$$

This hurts the phase margin by 16.3 degrees.

# Gain & Lag Compensator Design

Step 1: Pick a design rule for selecting the zero for your lag compensator (such as the zero will be 1/10 or 1/3 of the 0dB gain frequency.)

Step 2: Design a gain compensator with an extra 5.1 degrees (if using the 1/10 rule) or 16.3 degrees (if using the 1/3 rule) of phase margin. Determine the 0dB gain frequency.

Step 3: Add the lag compensator. This should bring the phase margin back to where you wanted it.

Example: Design a gain & lag compensator for  $G(s) = \left(\frac{2000}{s(s+5)(s+20)}\right)$  so that the system has a 40 degree phase margin.

Solution:

1) Assume the lag zero will be 1/10th of the 0dB gain frequency.

2) Find the frequency where the phase of G(s) is 45.1 degrees away fro 180 degrees (40 degree phase margin plus an extra 5.1 degrees).

$$G(j3.4983) = 4.6144 \angle -134.9^{\circ}$$

3) Add the lag compensator

$$K_{lag} = \left(\frac{s + 0.34983}{s + 0.034983}\right)$$

4) Crank up the gain until  $GK = 1 \angle -140^{\circ}$

$$GK = \left(\frac{2000}{s(s+5)(s+20)}\right) (k) \left(\frac{s+0.34983}{s+0.034983}\right)$$

$$GK(j3.4983) = 4.6372k \angle -140^{0}$$

$$k = 0.2156$$

and the compensator is

$$K(s) = \left(\frac{0.2156(s+0.34983)}{s+0.034983}\right)$$

Note that the DC gain is about 10x larger than what you obtained with gain compensator alone (a little less than 10x since you had to back off on the gain to get an extra 5.1 degrees of phase margin). The cost is a slightly slower system.

## Summary

The following table contrasts gain, lead, and lag compensators. Note that

- Gain compensators set the phase margin. Phase margin determines the resonance, damping ratio, percent overshoot, etc. as per the second order approximations.

- Lead compensators increase the phase margin

- Lead & Gain compensators speed up the system and increase the error constant (decreasing tracking error)

- Lag compensators greatly increase the error constant, but slightly slow down the system.

|                    | Gain           | Lead                                   | Lead & Gain                             | Lag & Gain                                          |

|--------------------|----------------|----------------------------------------|-----------------------------------------|-----------------------------------------------------|

| K(s)               | 0.2615         | $\left(\frac{2.615(s+4)}{s+40}\right)$ | $\left(\frac{7.2171(s+4)}{s+40}\right)$ | $\left(\frac{0.2156(s+0.34983)}{s+0.034983}\right)$ |

| Phase Margin       | 40 degrees     | 72 degrees                             | 40 degrees                              | 40 degrees                                          |

| 0dB Gain Frequency | 4.0031 rad/sec | 5.7165 rad/sec                         | 13.8325 rad/sec                         | 3.4983 rad/sec                                      |

| Kv                 | 5.23           | 5.23                                   | 14.43                                   | 43.12                                               |

#### **Comments on Lag Compensators**

My personal opinion is that lag compensators are not that useful.

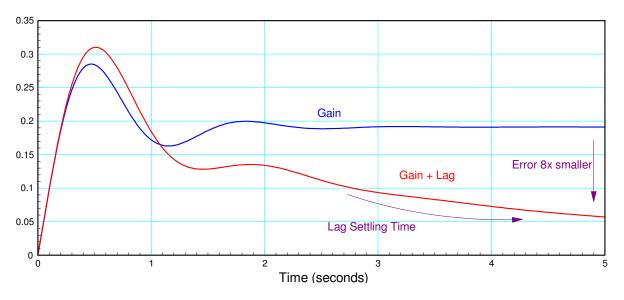

First, the lag pole and zero are really slow, almost by definition. For example, if you look at the steady-state error for a ramp input for a gain vs. lag compensator, the error looks like the following:

Error for a unit ramp input: Gain Compensation (blue) and Lag & Gain Compensation (red)

On the one hand, the lag compensator did it's job: the steady-state error is 8x smaller.

On the other hand, the 2% settling time is now 6 seconds due to the slow lag pole. What this means is

• In order for the lag compensator to have any affect on the system, the set point has to remain unchanging for at least 6 seconds.

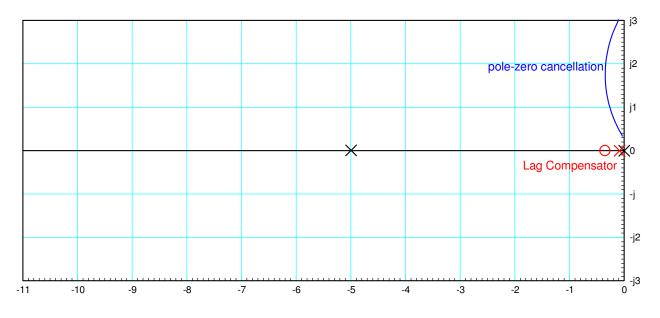

This also shows up on the pole-zero plot of the open-loop system

- At s = 0, the pole is 10x closer to s than the zero. The lag compensator increaes the DC gain by 10x (good).

- At s = j0.3 rad/sec and above, the lag compensator looks like pole-zero cancellation. The lag compensator has no affect on the steady-state error if the set point varies in any way.

The lag compensator only has an impact on the system if the set point is frequency-limited to 0.3 rad/sec

A second complaint I have about lag compensators is that I don't really see the point. With a lag compensator, the form of K(s) is

$$K(s) = \left(\frac{s+a}{s+a/10}\right)$$

The reason you place the pole at something small, like s = -0.035, is because on a Bode plot, you can't place a pole at s = 0: zero is off the chart when plotting on a log-scale. If you look at the root locus above, howver, there isn't much difference between placing the pole at s = -0.035 and s = 0.

If you move the pole from s = -0.035 to s = 0, however, the steady-state error becomes zero (rather than 8x smaller): it's now a type-2 system. So, why not just place the pole at s = 0?